1. paging

paging 은 주소공간을 페이지 단위로 다른다. 이는 많은 양의 정보를 필요로한다. 또, 각 가상 주소에 대해 추가 메모리 조회가 필요하다. 이 때 어떤 하드웨어 지원과 OS이 필요한가?

2. Translation-Lookaside Buffer (TLB)

MMU(메모리와 CPU에 관련되게 일하는 하드웨어)의 일부분이다. 이는 스스로는 아무것도 하지 못하고 OS가 이를 동작시켜줘야한다. Address-translation에 대한 캐시이다. 메모리까지 가서 table을 보기에는 오래걸리니까 캐시에 저장한다.

3. TLB의 기본 알고리즘

VPN = (VirtualAddress & VPN_MASK) >> SHIFT //상위 비트를 저장

(Success, TlbEntry) = TLB_Lookup(VPN) // 해당 VPN에 대한 TLB가 있는지 확인

if (Success == True) // TLB hit 찾았다!

if (CanAccess(TlbEntry.ProtectBits) == True) // 보안 정상적인지 확인

offset = VirtualAddress & OFFSET_MASK // 오프셋 알아내기

PhysAddr = (TlbEntry.PFN << SHIFT) | offset // 합체

Register = AccessMemory(PhysAddr) // 레지스터로 기기

else

RaiseException(PROTECTION_FAULT) // 예외

else // TLB miss 못찾았을 때는 paging 코드와 똑같다

PTEAddr = PTBR + (VPN * sizeof(PTE))

PTE = AccessMemory(PTEAddr)

if (PTE.Valid == False)

RaiseException(SEGMENTATION_FAULT)

else if (CanAccess(PTE.ProtectBits) == False)

RaiseException(PROTECTION_FAULT)

else

TLB_Insert(VPN, PTE.PFN, PTE.ProtectBits)

RetryInstruction()

4. TLB Miss 는 누가 처리해주나

1) 하드웨어가 알아서 처리, 그러기 위해서는 PTBR 꼭 필요 (넣어주는건 운영체제가 함)

2) OS 가 해결 (무한 연쇄 TLB 누락이 발생하지 않도록 주의)

5. TLB Contents

1) Fully associative

어떤 translation이던 빈공간이면 들어갈 수 있다.

원하는 곳이 있을 때 일일이 찾아서 들어감

2) VPN | PFN | other bits

-Valid bit, Protection bits, Address-space identifier, dirty bit

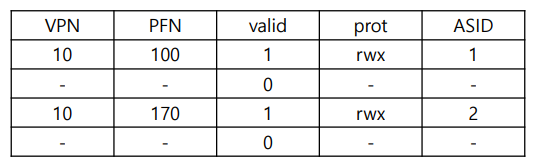

6. TLB의 context switch

1) 다른 프로세스에서 VPN이 같은 친구들이 있으면 헷갈림으로 ASID 지정

2) 메모리 오버헤드를 위해 페이지가 공유 되었을 때 동기화가 되지 않도록 노력

7. TLB 교체 정책 설계 방법

1) Least-Recently-Used (LRU)

최근에 잘 안쓰인 애는 나중에도 안쓰일거다 라는 논리. 안쓰는 친구랑 바꿔치기한다.

'학부 내용 정리 > [ 2-1 ] 운영체제' 카테고리의 다른 글

| [ OS ] Locks_slides (0) | 2022.06.12 |

|---|---|

| [ OS ] Concurrency and Thread (0) | 2022.06.11 |

| [ OS ] Paging (0) | 2022.04.18 |

| [ OS ] Segmentation (0) | 2022.04.18 |

| [ OS ] Address Spaces (0) | 2022.04.18 |